內存主導半導體行業,同時推動封裝工藝發展

2019年的Semicon大會上曝出不少有趣的消息。曾供職于英特爾、目前效力于Doller咨詢集團的Ed Doller表示,目前生產出的大多數晶體管都被用于內存技術領域,特別是DRAM與NAND閃存。下圖為他發給我的VLSI Research統計數據圖表。從2005年到2015年,NAND閃存的晶體管比例由34%增長至近80%。

在2019年的Semicon大會上,英特爾公司主辦了一場關注半導體封裝的特別活動。隨著傳統半導體規模的不斷放緩,芯片之間的具體封裝與通信方法,成為滿足2020年這十年當中大數據、物聯網以及人工智能等技術帶來的爆炸性需求增長的關鍵。目前,大部分高電流封裝設計的主要特征,在于采用更大的封裝級集成規模與SoC拆分。英特爾公司目前的部分重要目標在于開發新型技術,從而在封裝中將不同芯片對接起來以形成等同于SoC單片的功能。

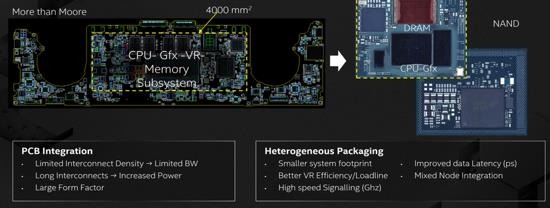

目前關于封裝技術的關注焦點包括:超薄/小尺寸客戶產品封裝(例如智能手機與可穿戴設備)、強大的交付架構、在使用高速信號時對發熱量的控制、芯片互連的密度與間距縮放、以及使用來自多個異構設備來源的多種設計等。下圖所示為英特爾方面發布的一份文稿,其中闡述了從傳統PCB集成到異構封裝(包括DRAM與NAND)的轉變。異構封裝使得電子元件的物理面積更小、能效更高且性能更強。

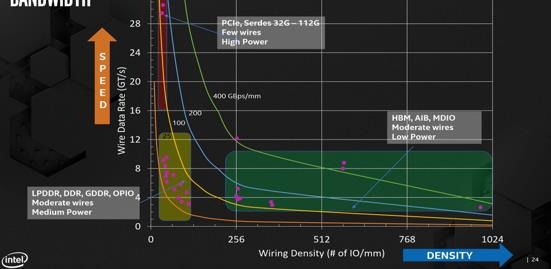

除了縮小集成電路的物理面積之外,目前的封裝工藝也越來越薄,這一點往往通過削薄并堆疊晶片、并在芯片背面構建某些結構的方式實現。此外,性能選項也在不斷增加。所謂帶寬密度,是指線數據速率乘以所謂布線密度(每毫米IO數值)所得出的結果,并以GBps/mm表示。下圖展示了幾種設備類型(特別是存儲設備)的帶寬密度。

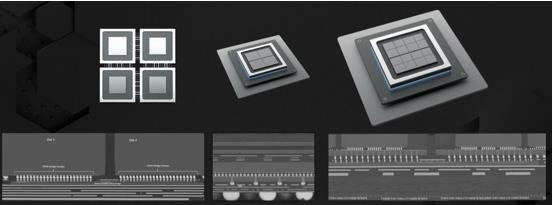

目前業界正從典型的有機封裝(FCGBA)轉向更為先進的超密度GCBGA(WIP),后者在有機基板上利用新型設備與光刻工藝以將IO/mm/層從23至48提升至64至256。采用嵌入式芯片的方法,代工廠能夠在EMIB高密度板的封裝之內采用密度極高的布線,其IO密度可以達到256至1024 IO/mm/層。此外,英特爾公司也一直在探索其3D芯片堆疊版本,并將此命名為Feveros。如下圖所示(含橫截面),Feveros可以與EMIB結合使用。

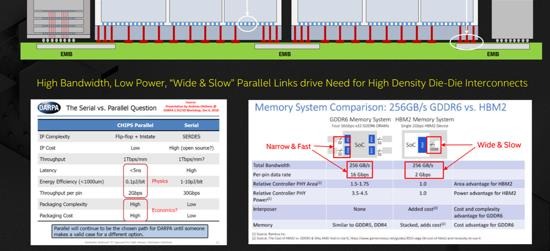

縮短處理器與存儲器之間的距離能夠顯著提高性能,這種設計在降低延遲以及提高功率效率方面體現得尤其突出。通過這種方式,我們不再需要將大量功率用于數據在處理器與存儲器之間的往來傳輸身上。英特爾公司致力于通過Feveros芯片堆疊等方式實現存儲器與處理器的集成。目前,高帶寬、低功率密集并行鏈路(例如高帶寬存儲器,簡稱HBM)的廣泛采用正在推動市場對于晶片間高密集互連的需求。

通過下圖可以看出,并行互連HBM能夠帶來遠優于串行互連DDR接口的低延遲與低功耗水平。這種高密度并行互連方法主要受到布線密度、鏈路長度、線寬、線與線之間間隔以及線之間電介質性質等因素的影響。

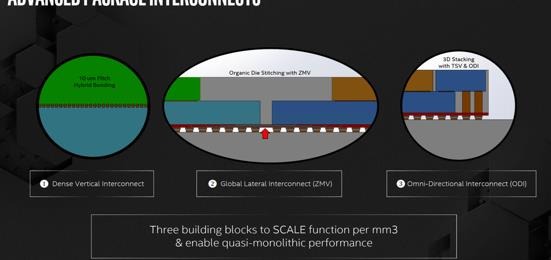

下圖總結了幾種能夠使處理器與存儲器盡可能貼近的多芯片互連方法,分別為高密度垂直互連、全校準通孔(ZMV)橫向互連以及全向互連(ODI)。

絕大多數半導體晶體管能夠支持多種內存技術,特別是DRAM與NAND。而英特爾方面在本屆Semicon大會上展示的各項高級封裝技術,則能夠進一步在內存與處理系統之間建立起高性能連接。

本文章選自《AI啟示錄》雜志,閱讀更多雜志內容,請掃描下方二維碼