XPU戰略縱深發展 英特爾展示多樣化的架構創新

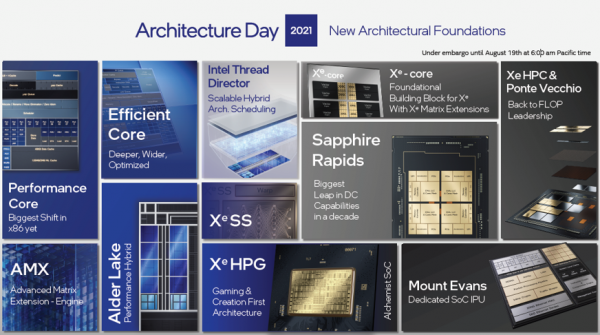

在工作負載多元化的今天,計算的多云化趨勢也非常明顯。在此背景下,英特爾提出了XPU的發展戰略。而在近日舉行的2021年英特爾架構日上,英特爾推出兩大x86 CPU內核、兩大數據中心SoC、兩款獨立GPU,以及變革性的客戶端多核性能混合架構,為我們完美呈現了XPU的產品組合。

英特爾公司中國區數據平臺集團總經理王飛告訴記者,未來數據中心計算架構的異構化趨勢非常明顯,英特爾提供廣泛的產品組合,“多點開花”也是為了給用戶更多的選擇。“因為一種產品可以適配各種工作負載已經變得不現實,所以我們希望提供多種產品,比如CPU、GPU、IPU等。而且英特爾提供如此眾多多樣化的產品也是用戶、客戶、OEM或者是CSP(云服務提供商)對我們提出了要求,給予他們更多的選擇”

我們知道英特爾此前一直強調六大技術支柱,那就是制程&封裝、架構、內存&存儲、互連、安全和軟件。對于英特爾而言,架構的重要性不言而喻。

在架構日上,英特爾公布了英特爾架構在近年來重大的改變和創新。 這包括:第一次深入介紹了英特爾首個性能混合架構Alder Lake,其搭載兩款新一代x86內核以及智能英特爾硬件線程調度器;英特爾全新引領行業標準的數據中心架構Sapphire Rapids,其搭載全新的性能核以及多種加速器引擎;英特爾全新的獨立游戲圖形處理器(GPU)架構;英特爾全新的基礎設施處理器(IPU)以及超凡的數據中心GPU架構Ponte Vecchio,其具備英特爾迄今為止最高的計算密度。

如此“一股腦”的架構更新,你看上去是不是眼花繚亂,別急,我們一一進行詳細說一下。

持續創新x86內核

眾所周知,英特爾是x86內核的引領者,這次英特爾對于原來的x86架構進行了創新,那就是進行了能效核和性能核的區分和集成。

具體來說,能效核是一個高度可擴展的x86微架構,它能滿足從低功耗移動應用到多核微服務的全方位計算需求。

此高能效x86微架構在有限的硅片空間實現多核任務負載,并具備寬泛的頻率范圍。該架構致力通過低電壓能效核降低整體功率消耗,為更高頻率運行提供功率熱空間。這也讓能效核提升性能,以滿足更多動態任務負載。

能效核可以利用各種技術進步,在不耗費處理器功率的情況下對工作負載進行優先級排序,并通過每周期指令數(IPC)改進功能直接提高性能。

對比英特爾迄今為止最多產的CPU微架構——Skylake,能效核可在相同功耗下提升40%的單線程性能,或者在提供同樣性能時,功耗僅為Skylake的40%不到。就吞吐量性能而言,與運行四個線程的兩個Skylake內核相比,四個能效核在性能提升80%的同時功耗更低,或者在提供相同吞吐量性能時,功耗降低80%。

而性能核不僅是英特爾迄今為止性能最高的CPU內核,而且在CPU架構性能方面實現階梯式提升,推動未來十年的計算發展。它是一個更寬、更深、更智能的架構,展現出更高的并行性,提高執行并行性,降低時延,提升通用性能。它還幫助支持大數據集和大型代碼體積的應用程序。與第11代酷睿架構(Cypress Cove內核)相比,相同頻率下,性能核在一系列工作負載上平均提升了約19%。

針對數據中心處理器和機器學習的發展趨勢,性能核提供了專用硬件,包括新的英特爾高級矩陣擴展(AMX)來執行矩陣乘法運算,以獲得數量級的性能——AI加速提升約8倍。這是為軟件易用性而設計,利用了x86編程模型。

同時,為了將能效核和性能核無縫銜接在一起,英特爾專門開發了英特爾硬件線程調度器,從開始就動態、智能地分配工作負載,從而優化系統以在真實場景中實現更高的性能和效率。

硬件線程調度器直接內置于硬件中,可提供對內核狀態和線程指令混合比的低級遙測,讓操作系統能夠在恰當的時間將合適的線程放置在合適的內核上。硬件線程調度器具有動態性和自適應性——它會根據實時的計算需求調整調度決策——而非一種簡單的、基于規則的靜態方法。

下一代至強處理器更“強”

對于數據中心市場,英特爾至強平臺是一個標桿。雖然在過去的一段時間,英特爾在數據中心的產品迭代備受業界議論,但是英特爾依然保持自己的節奏。

架構日上,下一代英特爾至強可擴展處理器(代號為“Sapphire Rapids”)的產品更新信息被披露。

Sapphire Rapids的核心是一個分區塊、模塊化的SoC架構,采用英特爾的嵌入式多芯片互連橋接(EMIB)封裝技術,在保持單晶片CPU接口優勢的同時,具有顯著的可擴展性。

Sapphire Rapids提供了一個單一、平衡的統一內存訪問架構,每個線程均可完全訪問緩存、內存和I/O等所有單元上的全部資源,由此實現整個SoC具有一致的低時延和高橫向帶寬。

Sapphire Rapids基于Intel 7制程工藝技術,采用英特爾全新的性能核微架構,該架構旨在提高速度,突破低時延和單線程應用性能的極限。同時,Sapphire Rapids集成了先進的內存和下一代I/O,包括PCIe 5.0、CXL 1.1、DDR5和HBM技術。

未來數據中心會越來越多面向微服務架構、異構計算以及AI計算加速,Sapphire Rapids提供了數據中心相關加速器,包括新的指令集架構和集成IP,以在各種客戶工作負載和使用中提升性能。新的內置加速器引擎包括:英特爾加速器接口架構指令集(AIA)、英特爾高級矩陣擴展(AMX)、英特爾數據流加速器(DSA)等。

特別是Sapphire Rapids中引入的新加速引擎——AMX,可為深度學習算法核心的Tensor處理提供大幅加速。其可以在每個周期內進行2000次INT8運算和1000次BFP16運算,實現計算能力的大幅提升。

英特爾技術專家告訴記者,英特爾充分認識到AI工作負載對數據中心的重要性,所以在AVX512的基礎上又專門設計了AMX加速集成的IP模塊,提供更高效的AI算力。

使用早期的Sapphire Rapids 芯片,與使用英特爾AVX-512 VNNI指令的相同微基準測試版本相比,使用新的英特爾AMX指令集擴展優化的內部矩陣乘法微基準測試的運行速度提高了7倍以上,為AI工作負載中的訓練和推理上提供了顯著的性能提升

千呼萬喚的GPU產品

在架構日上,英特爾也宣布了將推出的顯卡架構,包括面向消費者市場的Xe HPG微架構和面向數據中心市場的Xe HPC微架構,以及Alchemist SoC,Ponte Vecchio SoC。

Xe HPG是一款全新的獨立顯卡微架構,專為游戲和創作工作負載提供發燒級的高性能。Xe HPG微架構為Alchemist系列SoC提供動力,首批相關產品將于2022年第一季度上市,并采用新的品牌名——英特爾銳炫(Intel Arc)。 Xe HPG微架構采用全新的Xe內核,是一款聚焦計算、可編程且可擴展的元件。

Ponte Vecchio基于Xe HPC微架構,提供業界領先的每秒浮點運算次數(FLOPs)和計算密度,以加速AI、HPC和高級分析工作負載。英特爾公布了Xe HPC微架構的IP模塊信息;包括每個Xe核的8個矢量和矩陣引擎(稱為XMX Xe Matrix eXtensions);切片和堆棧信息;以及包括計算、基礎和Xe Link單元的處理節點的單元信息。

關于這兩種架構的顯卡詳細技術參數信息,我就不太一一列出了。這里需要需要指出的是,顯卡架構對于補齊英特爾XPU戰略具有重要意義,畢竟圖形處理以及AI類工作負載日漸流行的今天,GPU產品的需求是出繼續增加的。

王飛說,英特爾對于獨立顯卡的信心還是很強的,英特爾提供了OneAPI,可以把CPU和GPU很好地集成在一個系統之下,使軟件編程變得更容易,英特爾注重軟硬件的綜合實力。

另外,英特爾也非常重視生態圈,與客戶一起聯合創新,比如在IDM2.0的架構之下,GPU產品既可以采用英特爾自己的工廠進行生產,也可以通過臺積電工廠進行生產,靈活性更高。所以很多客戶其實非常期待英特爾的GPU產品。

展望未來,我們暫且不論英特爾顯卡的市場競爭表現如何,其戰略價值已經擺在那里,讓我們拭目以待。

基礎設施處理器(IPU)

IPU是一種可編程的網絡設備,旨在使云和通信服務提供商減少在中央處理器(CPU)方面的開銷,并充分釋放性能價值。

如這樣的定義,我們知道IPU與CPU的關系,比如云運營商可以將基礎設施任務卸載到IPU上,更大化實現CPU利用率和收益。

架構日上,英特爾介紹了首個ASIC IPU——Mount Evans,它是英特爾與一家一流云服務提供商共同設計和開發的,它融合了多代FPGA SmartNIC的經驗。例如Mount Evans使用硬件加速的NVMe存儲接口,該接口擴展自英特爾傲騰技術,以模擬NVMe設備;采用英特爾高性能Quick Assist技術,部署高級加密和壓縮加速;可使用現有普遍部署的DPDK、SPDK等軟件環境進行編程。

Oak Springs Canyon是一個IPU參考平臺,基于英特爾至強D處理器(Intel Xeon-D)和擁有業界領先的功率、效率、性能的英特爾Agilex FPGA構建。

王飛表示,在IPU方面,英特爾既提供ASIC又提供FPGA方案,一方面是給用戶提供多種可能性,另一方面這些產品更加兼容,英特爾可以在整體系統級別進行優化,客戶不需要整合不同家的產品,這是英特爾比較大的優勢。

結語

如今的半導體的產業已經早已不是“一招鮮吃遍天”的時代了,多樣化和不斷延展自身的邊界已經成為芯片廠商的主基調。而此次英特爾在架構日上的眾多創新產品公布,讓我們看到了英特爾在技術創新方面的持續迭代,隨著這些產品漸次落地,我們或將迎來全新的計算時代。

本文章選自《AI啟示錄》雜志,閱讀更多雜志內容,請掃描下方二維碼